將Allegro的brd板子導(dǎo)入Protel (DXP)中的詳細(xì)步驟

AD不支持導(dǎo)入allegro的brd文件�����,orcad的layout的max文件倒是支持�����,可是同為cadence的產(chǎn)品

2009-11-01 16:49:01 5431

5431 如何將dxf導(dǎo)入Allegro

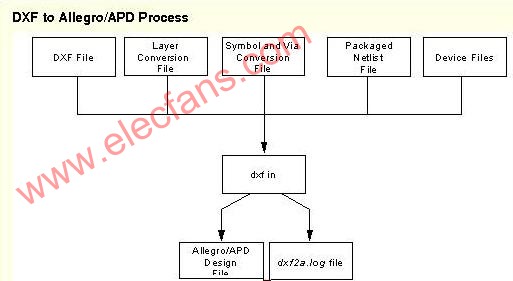

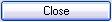

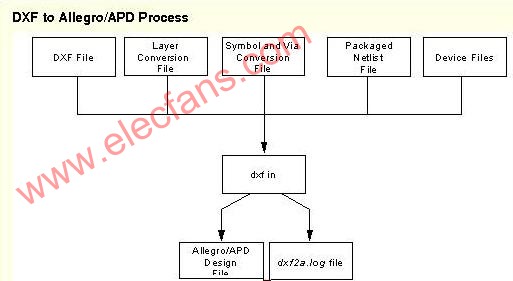

Allegro可以導(dǎo)入AutoCAD產(chǎn)生的DXF文件(支持DXF R10-R14版本)���。同時(shí)Allegro也可以將設(shè)計(jì)文

2010-03-21 18:21:00 11641

11641

Cadence Allegro如何對(duì)比兩份PCB文件差異 在進(jìn)行PCB設(shè)計(jì)的時(shí)候,有時(shí)候會(huì)需要對(duì)兩份PCB文件進(jìn)行對(duì)比����,以便核對(duì)前后修改后的文件,哪些地方有差異,我們這里講述一下

2022-12-23 18:30:07 2312

2312 ALLEGRO16.6中不同兩個(gè)PCB文件如何復(fù)制復(fù)制成同一個(gè)文件也就是在原文件上添加一部分電路����,添加這部分電路在另外一個(gè)文件中。通過(guò)復(fù)制或導(dǎo)入可以直接生成另外一個(gè)文件上電路已經(jīng)做好�,想把這個(gè)電路直接放置到原文件上�����。連接網(wǎng)絡(luò)部分通過(guò)原理圖導(dǎo)入網(wǎng)絡(luò)來(lái)實(shí)現(xiàn)互導(dǎo)可是���,不知道如何做

2015-03-10 14:33:35

1.用AD導(dǎo)入Allegro 17.X PCB文件�、保存為5.0 版本格式.pcbdoc2.用PADS,菜單導(dǎo)入命令��,選擇protel ***的.pcbdoc文件���,導(dǎo)入低版本的.asc文件3.用allegro導(dǎo)入pads的.asc文件

2019-11-29 21:40:07

我用Orcad導(dǎo)出netlist時(shí)成功了�,但是每次導(dǎo)入Allegro時(shí)就提示這個(gè)錯(cuò)誤��,我的封裝明明都已經(jīng)做好了,而且psm和pad的文件路徑也設(shè)置的沒(méi)有錯(cuò)����,哪位大神幫忙解決一下?謝謝啦�!急求!

2015-12-08 11:16:53

”—>“導(dǎo)入…”�,導(dǎo)入前面新建文件夾中的Allegro 文件(.brd)執(zhí)行轉(zhuǎn)換,等待轉(zhuǎn)換結(jié)束即可得到PADS 文件(.pcb)�����。執(zhí)行完后����,在Command中輸入:main out,回車����,這時(shí)

2019-09-17 09:05:03

我從一塊板子上導(dǎo)出的庫(kù)文件,單獨(dú)打來(lái)查看沒(méi)有任何問(wèn)題�,重新導(dǎo)入到原PCB也沒(méi)有錯(cuò)誤。但我想用到一塊新的PCB上,就是導(dǎo)不進(jìn)去����。查看日志文件����,提示can not find symbol。但我的庫(kù)文件

2017-04-15 09:49:38

將AD中的PCB文件轉(zhuǎn)換為PCB ASICII文件�����,然后導(dǎo)入到easyEDA�����,右下角顯示“正在連接服務(wù)器”�����,等一會(huì)就出現(xiàn)“錯(cuò)誤的文件類型”�,請(qǐng)問(wèn)這是怎么回事���?如何解決?

2017-03-29 18:40:43

Layout2Allegro來(lái)完成這項(xiàng)工作��?! ?) 在Protel中將PCB封裝放置到一張空的PCB中,并將這個(gè)PCB文件用Protel PCB 2.8 ASCII的格式輸出出來(lái)���; 2) 使用Orcad Layout導(dǎo)入

2018-09-17 17:14:49

PORTEL99 PCB編輯器的文件菜單中選擇導(dǎo)入CAD文件�����,把繪好了元件模型的CAD文件導(dǎo)進(jìn)去��,導(dǎo)入成功后, PORTEL 99 PCB編輯器就出現(xiàn)了元件封裝的基本圖形�����。 6. 再在PORTEL99 里新建一

2016-08-23 10:25:38

PORTEL99 PCB編輯器的文件菜單中選擇導(dǎo)入CAD文件����,把繪好了元件模型的CAD文件導(dǎo)進(jìn)去,導(dǎo)入成功后�����, PORTEL 99 PCB編輯器就出現(xiàn)了元件封裝的基本圖形�����。 6. 再在PORTEL99 里新建一

2016-09-10 10:05:33

一個(gè)PCB文件�����,再在PORTEL99 PCB編輯器的文件菜單中選擇導(dǎo)入CAD文件�����,把繪好了元件模型的CAD文件導(dǎo)進(jìn)去��,導(dǎo)入成功后����, PORTEL 99 PCB編輯器就出現(xiàn)了元件封裝的基本圖形��。 6.

2017-10-07 14:47:55

netin.log文件中沒(méi)有error為止����,才完成原理圖網(wǎng)表成功導(dǎo)入PCB設(shè)計(jì)工具。以上便是PCB設(shè)計(jì)軟件allegro操作中網(wǎng)表導(dǎo)入的常見(jiàn)錯(cuò)誤�,下期預(yù)告:封裝調(diào)入及常見(jiàn)錯(cuò)誤�����,請(qǐng)同學(xué)們持續(xù)關(guān)注【快點(diǎn)兒PCB學(xué)院】�。

2018-08-06 11:05:50

`PCB設(shè)計(jì)軟件allegro藍(lán)牙音箱案例實(shí)操講解���,以藍(lán)牙音箱為案例將PCB設(shè)計(jì)基礎(chǔ)知識(shí)融進(jìn)實(shí)際案例中��,通過(guò)操作過(guò)程講解PCB設(shè)計(jì)軟件功能及實(shí)用經(jīng)驗(yàn)技巧��,全文著重講解網(wǎng)表導(dǎo)出導(dǎo)入和封裝路徑設(shè)置

2018-07-31 14:15:07

allegro .brd文件轉(zhuǎn)成AD .pcbdoc文件�,1�����、將.brd文件生成.alg文件2��、使用AD導(dǎo)入向?qū)?alg文件生成 .pcbdoc文件最后顯示圖片內(nèi)容�,誰(shuí)能解答一下

2022-03-23 11:14:19

allegro pcb desiger 導(dǎo)入網(wǎng)表文件出現(xiàn)這個(gè)問(wèn)題,放置元件cannot load symbol'封裝名'庫(kù)的路徑設(shè)置沒(méi)問(wèn)題����。

2017-01-09 22:10:39

allegro導(dǎo)入DXF板后,錯(cuò)誤操作直接將DXF線段shape板框�����,發(fā)現(xiàn)后我直接將DFX全部刪掉,重新導(dǎo)入DFX為什么導(dǎo)入不成功了����?是什么原因,是我操作問(wèn)題嗎����?請(qǐng)大神指教

2019-08-06 04:27:50

求助各位大神:小弟初學(xué)allegro ,我用allegro導(dǎo)入網(wǎng)表時(shí)總是提醒Symbol 'SOT23' for device 'TR3_SOT23_TR3' not found

2014-08-29 11:31:17

我想知道如何將AD的PCB封裝庫(kù)導(dǎo)入到allegro中�,還有AD的原理圖的網(wǎng)表如何導(dǎo)入到allegro中,我想知道如何將AD的PCB封裝庫(kù)導(dǎo)入到allegro中�����,還有AD的原理圖的網(wǎng)表如何導(dǎo)入到allegro中

2016-10-13 17:16:12

�,各種封裝都繪好后,就要將其轉(zhuǎn)到PORTEL 99里再作加工了��?! ?. 打開PORTEL99���,先新建一個(gè)PCB文件,再在PORTEL99 PCB編輯器的文件菜單中選擇導(dǎo)入CAD文件�,把繪好了元件模型

2017-06-22 16:52:57

portel的PCB文件可以如何導(dǎo)入allegro[hide]1.我所用軟件ad6.8(altium desigener6.8) 和spb16.02.在ad6.8里打開一個(gè)PCB圖后點(diǎn)文件- 另存為

2010-03-18 14:43:50

導(dǎo)入PADS ASCII PCB文件操作小貼士經(jīng)常有用戶在導(dǎo)入PADS ASCII 文件時(shí)可能遇到一些常見(jiàn)文件格式轉(zhuǎn)換問(wèn)題。為此�����,我們特別總結(jié)了一些處理流程來(lái)解決它們�。 常見(jiàn)問(wèn)題:在文件導(dǎo)入過(guò)程中

2013-07-11 15:31:59

AD19導(dǎo)入Allegro文件提示allegro未安裝,怎么解決����?電腦已經(jīng)正常安裝allegro并可以打開待轉(zhuǎn)換文件。

2019-07-17 14:31:03

(不太好找)進(jìn)行轉(zhuǎn)換�����。DFL模式與正常.PCB模式下主要是文件可否導(dǎo)出的區(qū)別等(Pads-Allegro)Pads下有轉(zhuǎn)換工具�����,直接導(dǎo)出為*.hkp�,比allegro直接����、方便多。轉(zhuǎn)換細(xì)節(jié)方面就不

2014-11-27 10:02:08

ALTIUM怎么打開cadence allegro設(shè)計(jì)的的pcb文件

2014-10-28 11:48:17

Ad導(dǎo)入allegro的PCBbrd文件報(bào)錯(cuò)�����,如下圖 不知道什么原因

2019-05-27 00:23:08

Allegro PCB轉(zhuǎn)Allegro PCB:(1)把Altium Designer PCB轉(zhuǎn)換成PADS PCB�,并且導(dǎo)出5.0版本的ASC文件。(2)然后打開Allegor Designer

2019-11-21 14:12:49

AD的pcb設(shè)計(jì)文件并不能直接轉(zhuǎn)換成allegro的pcb板�����,常用的方法是AD→PADS→Allegro���;所以AD轉(zhuǎn)allegro的步驟如下:一�����、將AD文件轉(zhuǎn)為PADS文件���;(PADS9.5以上版本

2019-09-03 17:02:30

DXF文件導(dǎo)入ALLEGRO中的方法

2015-05-13 13:36:02

本帖最后由 Andyxiesz 于 2012-6-22 00:48 編輯

G41 Allegro PCB 文件16.5 文件哦《== 非常抱歉,忘記上傳最后一個(gè)文件�!==》 本人留有QQ,大家

2011-11-11 00:26:05

ALLEGRO的brd文件 課題組其他人都用ALLEGRO�,我一個(gè)人死撐著用AD。共享設(shè)計(jì)時(shí)原理圖還方便導(dǎo)入���,PCB文件麻煩了����,于是一直在找如何從AD中導(dǎo)入ALLEGRO的brd文件的方法�,一直未果(曾經(jīng)找了

2014-12-03 15:05:29

`想把a(bǔ)d13的pcb文件轉(zhuǎn)allegro命令欄報(bào)錯(cuò),補(bǔ)丁版本114�,求解,謝謝`

2019-02-27 17:53:59

本帖最后由 糖果. 于 2016-12-19 15:22 編輯

Altium Designer13.3.4導(dǎo)出網(wǎng)表���,allegro16.6通過(guò)other導(dǎo)入導(dǎo)入后出現(xiàn)error生成了device�����,setup中路徑已添加�,求問(wèn)如何解決

2016-12-19 14:32:45

Altium Designer,Allegro PCB(brd文件)需要通過(guò)其他一些途徑實(shí)現(xiàn)��,以Altium Designer 6.6為例介紹將Allegro的brd板子導(dǎo)入AD中�。基本思想是用CAM文件

2019-06-15 08:00:00

cadence allegro 16.5軟件pcb導(dǎo)入網(wǎng)表時(shí)出現(xiàn)以下錯(cuò)誤,導(dǎo)致導(dǎo)入失敗�,無(wú)法添加和預(yù)覽封轉(zhuǎn)元件,求大神解答

2015-12-16 13:37:08

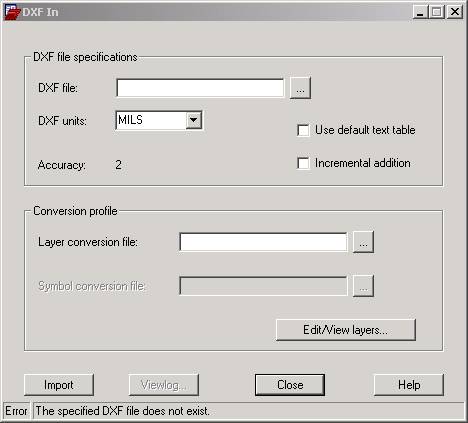

在開始菜單中�����,找到程序 PCB EDitor 6.0一定要打開這個(gè)軟件���,而不是直接打開一個(gè)已經(jīng)設(shè)計(jì)好的PCB文件后導(dǎo)入�����。是要直接打開軟件��,生成一個(gè)空的PCB文件��。再在菜單欄上��,選擇如下菜單這里選擇

2022-10-01 20:23:51

《Cadence Allegro實(shí)戰(zhàn)攻略與高速PCB設(shè)計(jì)》基本信息作者: 杜正闊 高寶君 何宗明 叢書名: EDA精品智匯館出版社:電子工業(yè)出版社ISBN:9787121284724上架時(shí)間

2017-08-11 17:11:31

(1)把Altium Designer PCB轉(zhuǎn)換成PADS PCB,并且導(dǎo)出5.0版本的ASC文件����。(2)打開Allegro PCB Editor,執(zhí)行菜單命令“Import-CAD

2021-08-06 09:51:39

1.方法1在PADS的Import界面中,如圖6-272所示��,選擇導(dǎo)入格式“Allegro Board files(*.brd)”���,選擇需要轉(zhuǎn)換的PCB����,即可開始轉(zhuǎn)換。稍微查看一下轉(zhuǎn)換過(guò)程中的警告

2021-08-10 16:08:34

本帖最后由 z00 于 2014-11-18 16:09 編輯

Altium Designer Summer08以后的版本中文檔導(dǎo)入向?qū)еС?b class="flag-6" style="color: red">Allegro PCB設(shè)計(jì)文件格式(.Brd)或

2014-11-18 15:48:32

封裝的焊盤文件�;Psmpath:指定封裝的psm文件; Allegro軟件導(dǎo)入網(wǎng)表以后�,為什么在PCB板上看不到元器件呢? 圖6-37 封裝庫(kù)路徑指定示意圖 第三步���,指定好封裝庫(kù)路徑之后�����,進(jìn)行

2020-09-07 17:23:05

關(guān)于PCB EDITOR 中導(dǎo)入DXF文件的問(wèn)題我使用的版本是Cadence 16.3����,電路板布線完成�����,未鋪地����,還需要添加漢字,以下是我的操作步驟:1:從PCB EDITOR中導(dǎo)出DXF文件�,我只

2013-04-28 07:14:51

在allegro中出gerber文件和CAM350中導(dǎo)入cuijianw適用范圍: CadenceAllegro 15.2 MentorCAM350 8.7 正文:準(zhǔn)備工作: 為了保證出片的正確性

2012-03-29 22:48:20

AD 不支持導(dǎo)入allegro的brd文件�����,orcad的layout的max文件倒是支持���,可是同為cadence的產(chǎn)品��,居然layout不能導(dǎo)入 brd��。我算是一個(gè)準(zhǔn)超級(jí)AD fans����,經(jīng)過(guò)自己

2019-07-23 07:00:19

有什么方法可以將Allegro的brd文件導(dǎo)入Protel中嗎�����?

2021-04-25 09:46:26

allegro設(shè)計(jì)的PCB文件,在Altium designer中導(dǎo)入時(shí)出現(xiàn)file:///C:\Users\Administrator.WIN7U-20140427E\Documents

2019-09-16 08:12:56

LAYOUT(.pcb) To allegro(.brd)2.2 PADS 和protel 和P-CAD 文件之間的轉(zhuǎn)換可以用AD6.9 完成原理圖PADS logic(.sch) To orCAD(.dsn

2019-07-08 08:29:59

問(wèn)大伙個(gè)問(wèn)題 allegro怎么打開orcad的PCB文件(.MAX后綴的)

2019-07-18 05:35:23

請(qǐng)高手指點(diǎn)如何將.DXF文件導(dǎo)入到Allegro pcb aditor中���? 是否還可以導(dǎo)入其他格式的板框文件���?

2010-12-22 22:58:45

如題,PCB或Gerber文件如何導(dǎo)入ProE���?

2012-05-09 11:28:55

allegro16.6PCB中Long Name Size: Change the # to 255已經(jīng)設(shè)置pcbenv文件中 set ALLEGRO_LONG_NAME_SIZE = 255set

2018-11-26 16:28:05

請(qǐng)問(wèn)原子老師����,我在ADI公司官網(wǎng)上下載到的ADN8830芯片封裝,怎樣導(dǎo)入Portel里

2019-03-18 06:35:55

大家好��,這是一個(gè)請(qǐng)求而不是一個(gè)問(wèn)題����。Xilinx能否以適合Altium導(dǎo)入的方式提供VC709的設(shè)計(jì)文件?目前只有“Allegro二進(jìn)制PCB設(shè)計(jì)文件(* .brd)”可供下載�����。但是����,如果您

2019-09-06 10:43:21

`高速PCB設(shè)計(jì)allegro軟件操作導(dǎo)入網(wǎng)表的兩種方法方法一:用Cadence自帶的原理圖OrCADCapture打開原理圖�����;單擊圖按鈕或執(zhí)行菜單命令Tools/Create Netlist

2017-02-08 10:32:23

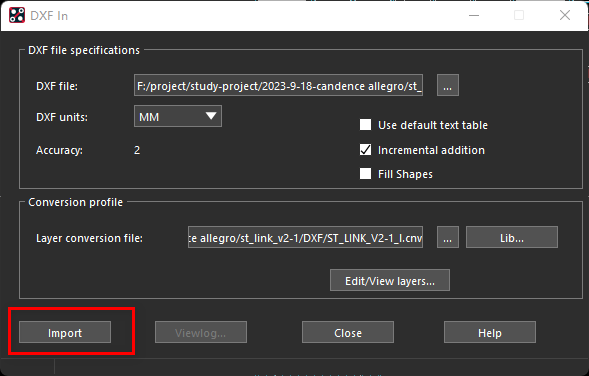

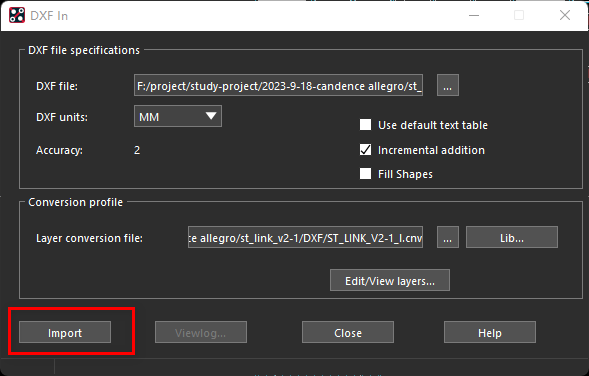

如何使用高速PCB設(shè)計(jì)軟件allegro將結(jié)構(gòu)圖導(dǎo)入到其中呢�,具體的操作步驟是怎樣的?結(jié)構(gòu)圖導(dǎo)入后的效果怎樣...都在這節(jié)中體現(xiàn)~一�����、識(shí)別結(jié)構(gòu)圖中的標(biāo)識(shí)說(shuō)明進(jìn)行結(jié)構(gòu)圖導(dǎo)入之前先了解下標(biāo)識(shí)說(shuō)明��,直觀感受結(jié)構(gòu)

2017-02-15 14:40:44

Allegro PCB Design

2008-10-16 09:37:38 0

0 ALLEGRO PCB SI L, XLALLEGRO PCB PI OPTION XLCadence Allegro PCB SI offers an integrated high-speed

2008-10-16 09:45:20 0

0 ALLEGRO PCB LIBRARIAN 610AUTOMATED LIBRARY PART CREATION AND VALIDATIONCadence Allegro PCB

2008-10-16 09:55:40 0

0 ALLEGRO生成鉆孔文件的方法

生成鉆孔文件的步驟:ALLEGRO TO NC DRILL

1. Manufacture -> NC -> Drill Customization…

2008-03-22 15:45:26 8020

8020

Allegro如何調(diào)用AutoCAD產(chǎn)生的數(shù)據(jù)教程

Allegro可以導(dǎo)入AutoCAD產(chǎn)生的DXF文件(支持DXF R10-R14版本)��。同時(shí)Allegro也可以將設(shè)計(jì)文件導(dǎo)出為DXF文件����,供其

2009-04-15 00:42:01 1921

1921

Allegro PCB設(shè)計(jì)流程一

Allegro PCB SI 的設(shè)計(jì)流程包括如下六個(gè)步驟:

Pre-Placement

&nbs

2009-11-18 10:17:00 2580

2580 Allegro生成鉆孔文件的步驟

生成鉆孔文件的步驟:ALLEGRO TO NC DRILL

1. Manufacture -> NC -> Dr

2010-03-21 18:11:19 4569

4569

本Allegro文件查看器可查看Allegro 輸出的文件,如Gerber文件以及設(shè)計(jì)文件等信息��,是Allegro free viewer 14.0的版本���。

2011-02-13 11:27:58 1

1 Altium Designer 導(dǎo)入powerPCB中的pcb文件

2017-03-01 21:53:29 0

0 到 5版不必回到 3.5版。 1. 打開Allegro 2. 執(zhí)行菜單File》Import》PADS 出現(xiàn)下面對(duì)話框 a.要導(dǎo)入板子的ASCII文件路徑�����,可以用Browse瀏覽查找 b.設(shè)置參數(shù)文件����,可以用

2017-12-05 11:49:37 0

0 AD封裝轉(zhuǎn)ALLEGRO封裝時(shí),要把所有封裝放到一張PCB上或者分批次的放到PCB上�����,把PCB轉(zhuǎn)成ALLEGRO格式的�����,然后再用ALLEGRO導(dǎo)出PCB封裝

2018-04-05 17:06:00 47055

47055

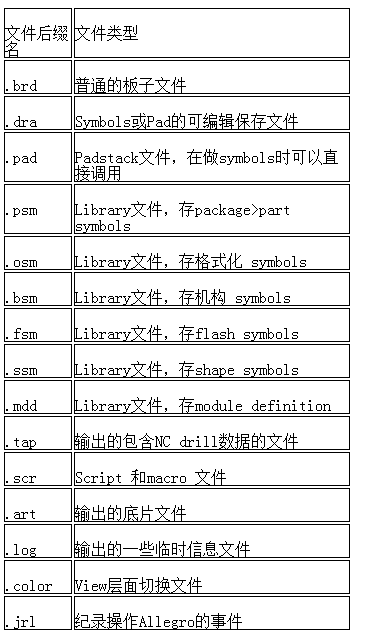

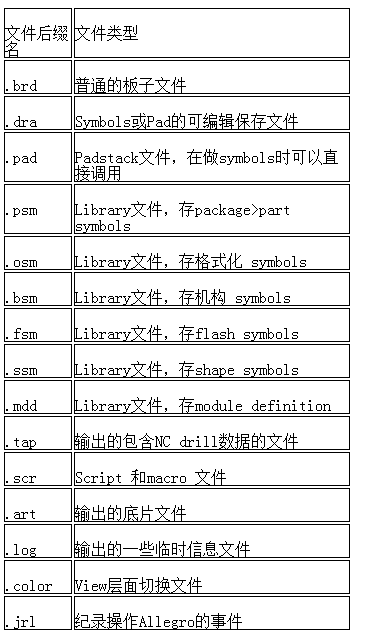

Allegro根據(jù)不同性質(zhì)功能的文件類型保存不同的文件后綴 allegro安裝后自帶的庫(kù)文件路徑是:C:/Cadence/SPB_15.5/share/PCB/PCB_lib/symbols

2018-04-25 15:44:00 6191

6191

本資料主要講述了Allegro設(shè)計(jì)從入門到速成���,從pcb導(dǎo)入到光繪文件導(dǎo)出全過(guò)程設(shè)計(jì)操作�����。

2018-11-12 08:00:00 0

0 EDA工程師在PCB設(shè)計(jì)過(guò)程中���,往往需要與結(jié)構(gòu)工程師打交道�,結(jié)構(gòu)圖紙即DXF文件就是結(jié)構(gòu)工程師與EDA工程師溝通的媒介��。本文針對(duì)Allegro導(dǎo)入DXF文件的詳細(xì)過(guò)程做詳細(xì)說(shuō)明���,本人看到網(wǎng)上大部分相關(guān)文章寫得都比較糟糕���,所以撰寫本文以便更好地幫助讀者解決問(wèn)題�。

2019-05-26 09:24:09 13710

13710

在PCB設(shè)計(jì)過(guò)程中,EDA工程師常常需要匹配兩代PCB的結(jié)構(gòu)���,這種情況下��,將上一代PCB的Outline(板框)導(dǎo)入新的PCB設(shè)計(jì)文件中�����,就可以大大縮短時(shí)間�,而且尺寸完全準(zhǔn)確。我看到常常有網(wǎng)友檢索類似的信息����,所以打算圖文并茂的方式為讀者講解Allegro中導(dǎo)入Outline的方法。

2019-06-16 10:11:46 6866

6866

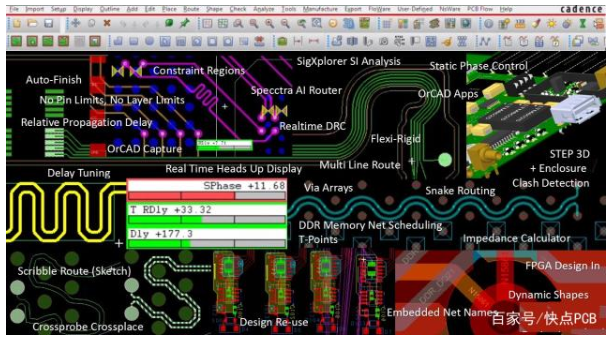

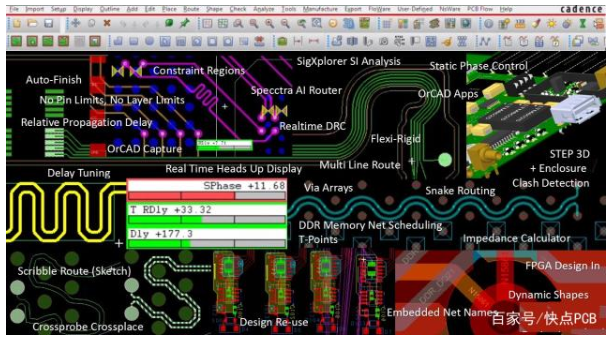

Allegro是Cadence推出的先進(jìn) PCB 設(shè)計(jì)布線工具����,也是目前最高端、最主流的PCB軟件代表之一�����,華為�、中興這類大型公司使用的也是Allegro。

2019-10-11 16:40:38 8617

8617

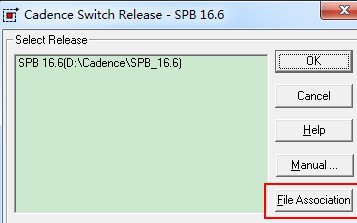

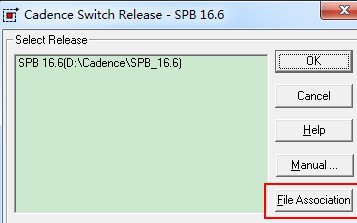

設(shè)計(jì)好的SCH和pcb文件我都需要先打開軟件�,通過(guò)軟件才能打開工程文件,allegro 不能設(shè)置成默認(rèn)打開方式

2019-10-13 09:27:00 18227

18227

如果能將AD或Power Logic原理圖產(chǎn)生的網(wǎng)表轉(zhuǎn)成Allegro格式的網(wǎng)表�����,那就能導(dǎo)入Allegro里面設(shè)計(jì)了�����,就不需要轉(zhuǎn)換原理圖了,省事又省時(shí)�����,這是最為簡(jiǎn)單方便又靠譜的方法了����。

2019-11-26 14:50:08 16583

16583 本文檔的主要內(nèi)容詳細(xì)介紹的是PCB設(shè)計(jì)軟件Allegro的學(xué)習(xí)教程免費(fèi)下載包括了:Allegro學(xué)習(xí)筆記之1——導(dǎo)出Gerber文件和鉆孔數(shù)據(jù)文件,Allegro學(xué)習(xí)筆記之2——覆銅����,Allegro

2020-05-15 08:00:00 0

0 PCB原理圖導(dǎo)入的2種方法,小白也能看懂����! Altium Designer的原理圖設(shè)計(jì)導(dǎo)入PCB,存在兩種方法:一種是直接導(dǎo)入法����,類似于Allegro的第一方導(dǎo)入;另一種是間接法����,即網(wǎng)表對(duì)比導(dǎo)入

2020-10-16 09:58:24 77092

77092

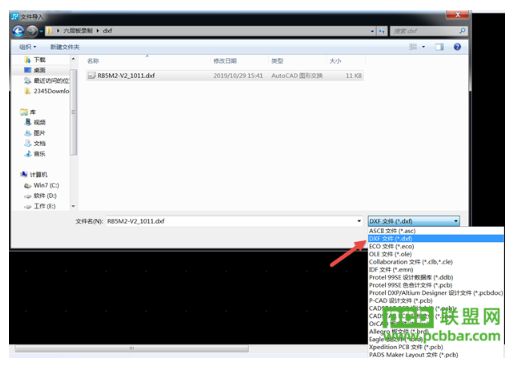

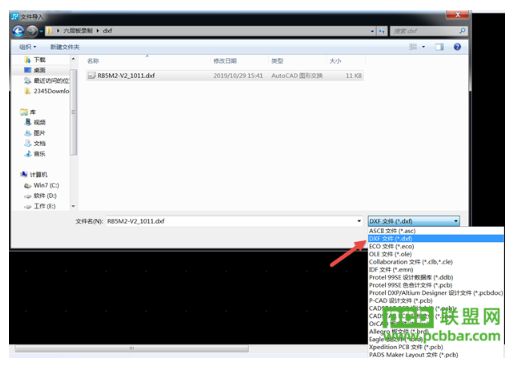

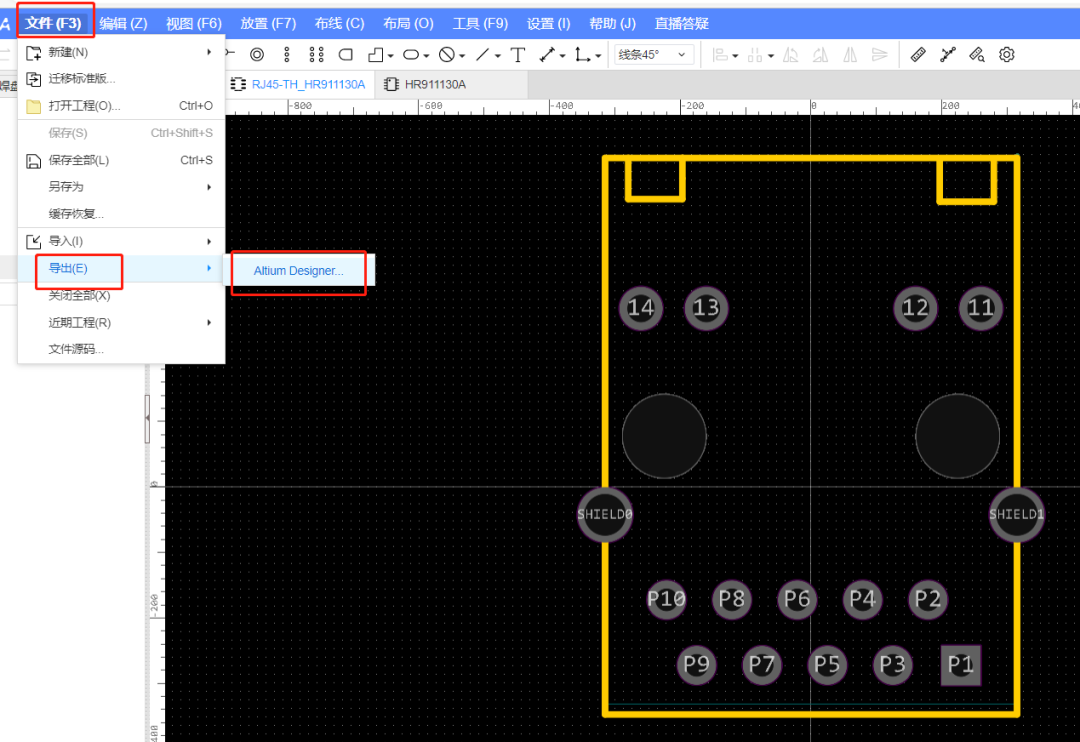

菜單欄中選擇【文件】-【導(dǎo)入】����,彈出的對(duì)話框中導(dǎo)入格式選擇 DXF文件(*.eco),然后選擇要導(dǎo)入的文件����,如圖1-1所示���; 圖1-1 導(dǎo)入類型選擇 #216;二步�,點(diǎn)擊打開�,彈出DXF導(dǎo)入對(duì)話框,如圖1-2所示�; 圖1-2 DXF導(dǎo)入 #216;第三步,在層選擇區(qū)域中的【可用】是在PCB板中所有可以用到

2020-10-20 09:36:51 14112

14112

Allegro導(dǎo)入dxf使用Z-Copy提示”Not a closed polygon or CLine. Element ignored����!”解決辦法

2021-05-10 09:48:16 0

0 Allegro常用的PCB封裝介紹。

2022-06-06 14:31:13 0

0 Allegro在導(dǎo)入網(wǎng)表文件時(shí)或者運(yùn)行軟件的時(shí)候出現(xiàn)如下截圖報(bào)錯(cuò)��,很多網(wǎng)友找不到解決方法�����,其實(shí)是可以根據(jù)下面?zhèn)z種方法去解決這個(gè)問(wèn)題的�����。

2022-10-11 09:12:57 6834

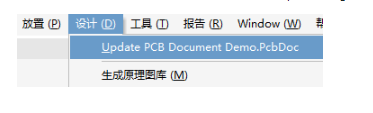

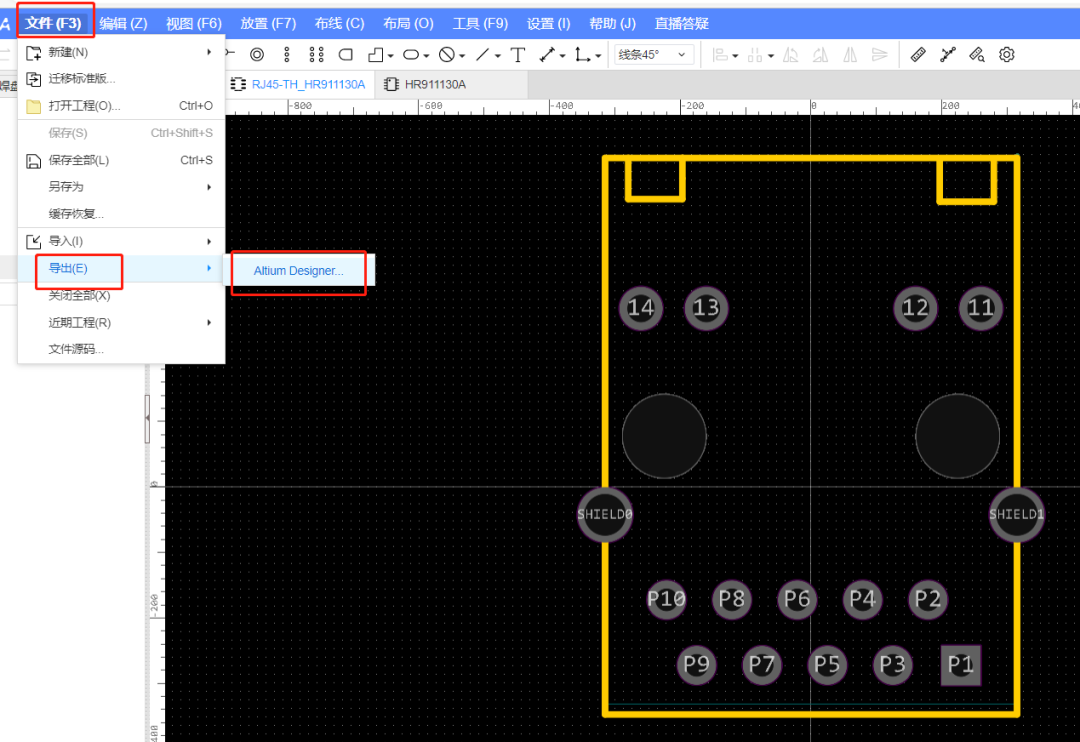

6834 怎樣把立創(chuàng)的PCB轉(zhuǎn)成allegro的

2023-04-03 10:02:37 3776

3776

創(chuàng)建一個(gè)項(xiàng)目關(guān)聯(lián)導(dǎo)入后的OrCAD Schematic項(xiàng)目和PADS/Allegro PCB項(xiàng)目。

2023-06-05 11:50:22 1479

1479

Cadence Allegro 22.1-1-1-導(dǎo)入DXF板框詳細(xì)步驟

2023-09-25 09:09:35 2239

2239

Allegro輸出Gerber文件

2022-12-30 09:19:40 6

6 Allegro輸出光繪文件規(guī)范

2022-12-30 09:19:41 3

3

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論