聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1630文章

21801瀏覽量

606322 -

定時

+關(guān)注

關(guān)注

1文章

122瀏覽量

25519 -

計數(shù)器

+關(guān)注

關(guān)注

32文章

2276瀏覽量

95041

發(fā)布評論請先 登錄

相關(guān)推薦

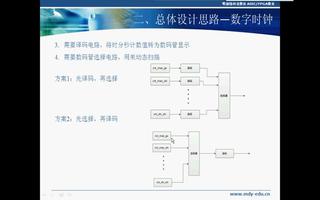

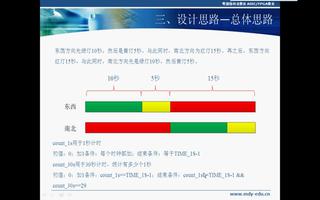

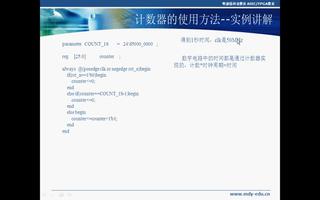

明德?lián)P點(diǎn)撥FPGA課程---第十三章 ?計數(shù)器的使用

第十三章計數(shù)器的使用1. 計數(shù)器使用原則2. 計數(shù)器練習(xí)13. 計數(shù)器

發(fā)表于 10-30 10:15

環(huán)形計數(shù)器和扭環(huán)形計數(shù)器

環(huán)形計數(shù)器和扭環(huán)形計數(shù)器

移位寄存器也可以構(gòu)成計數(shù)器,稱為移位型計數(shù)器。它有兩種結(jié)構(gòu):環(huán)形計數(shù)器

發(fā)表于 01-12 14:07

?9873次閱讀

基于FPGA的PWM計數(shù)器改進(jìn)設(shè)計

簡單改變FPGA計數(shù)器規(guī)格使作為DAC功能PWM計數(shù)器的紋波降低。

發(fā)表于 04-06 11:11

?2003次閱讀

HL配套C實驗例程100例之計數(shù)器計數(shù)

HL配套C實驗例程100例之計數(shù)器計數(shù),配合開發(fā)板學(xué)習(xí)效果更好。

發(fā)表于 04-11 16:09

?4次下載

定時器之計數(shù)器應(yīng)用

之計數(shù)器應(yīng)用。概述計數(shù)器是對外來脈沖信號計數(shù),對來自于外部引腳P3.4(T0),P3.5(T1),P1.1(T2)的外部信號計數(shù)。在設(shè)置

發(fā)表于 02-21 11:06

?1773次閱讀

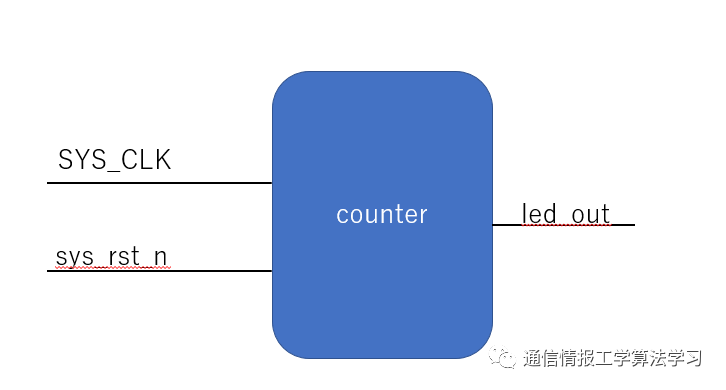

FPGA基礎(chǔ)應(yīng)用計數(shù)器的實例詳細(xì)說明

該計數(shù)器從0 計數(shù)到4294967295,然后回滾到0 并重新開始計數(shù)。它只需要FPGA 上一點(diǎn)點(diǎn)的資源就可以迅速完成計數(shù),這都多虧了

發(fā)表于 12-11 17:26

?12次下載

基于FPGA的十進(jìn)制計數(shù)器

本方案是一個基于 FPGA ?的十進(jìn)制計數(shù)器。共陽極 7 段顯示器上的 0 到 9 十進(jìn)制計數(shù)器,硬件在 Xilinx Spartan 6 FPGA

發(fā)表于 12-20 14:52

?2次下載

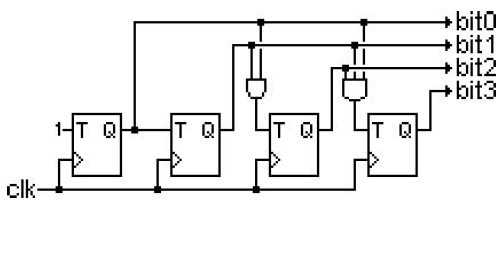

時序邏輯電路設(shè)計之計數(shù)器

前面已經(jīng)學(xué)習(xí)了時序邏輯電路中的基本單元:觸發(fā)器,這次就用其來整點(diǎn)活,實現(xiàn)計數(shù)器的設(shè)計,計數(shù)器可以說是任何和時序有關(guān)的設(shè)計都會用到他。

FPGA之計數(shù)器的練習(xí)(1)

FPGA之計數(shù)器的練習(xí)(1)

評論